2 MB DAT PCB

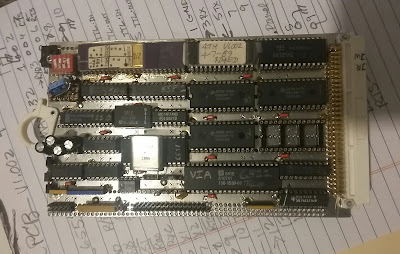

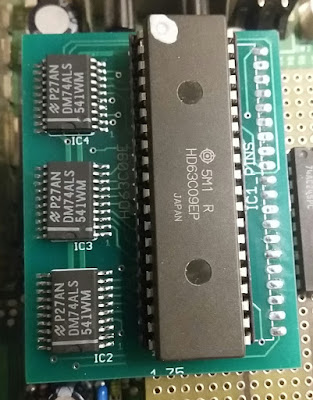

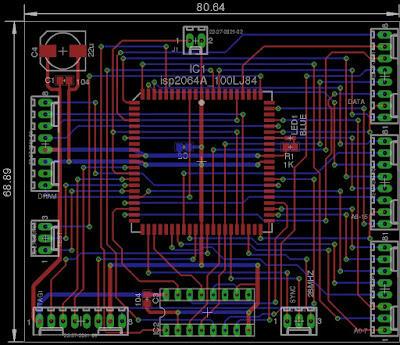

Here is the beginnings of a 2 to 8 MB DAT PCB. Think NoCan series. Update: June/18/2018 I can now edit the schematics and program Lattice 2064A-100LJ84 CPLD's. Here is a beginning of a new "set" of 2MB CoCo3 DAT pcb's. IC on the bottom is the 16x2bit SRAM for $FFAX D6 and D7. Yup, it's a mystery. Actually, these two chips can be added to the "Isolator" pcb making a lot of wiring easier. Older stuff below: Started with a CPU isolator, added 3.3V regulator, and a Lattice lcMACH-4128V CPLD. Not done yet. The blue area under the CPLD is it's own ground plane. I may just make a separate CPLD PCB then wire it to the current Isolator. This PCB creates ZA9 and ZA10 for expanded memory. ZA9 is like the 2MB setup that has been used in the past. The ZA10 portion is new and will expand the memory more than the 2MB. The CPLD has the 16x2 sram inside. Connectors: Upper left is the ZA9, ZA10 connection to the Memory...