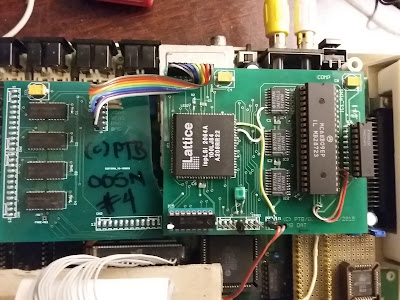

8MB setup for a Tandy CoCo3

Years ago the NoCan series of add-on PCB's was developed. Now today with more resources available to use, the NoCan-8MB is back. The first go-around is a prototype unit only. Updated: Aug/30/2018 Here is a single picture of the current setup. Since the PCB layout limits the size of any PCB, it's in two pieces currently. A memory PCB (left PCB) and a DAT PCB. It started with the 2MB setup and received some hand-added wires to use up the rest of that 16 x 4 SRAM (74LS189). The 8-wire cable at the bottom of the DAT PCB (right PCB) is the JTAG connection. It was tested with Robert Gault's memory test software, originally designed strictly for the NoCan-8MB boards. Thanks Robert! I used the same memory PCB and stuffed another DAT PCB to test an 8MB CPLD. How to use the extra 6MB in a NoCan-8MB device. The following initializes a ramdisk already named "/r0" (/rzero), and fills it with the contents of /DD/CMDS. <enter> Means ...