2MB Setup for a Tandy CoCo-3

The 2MB system runs and NitrOS-9 6809E works.

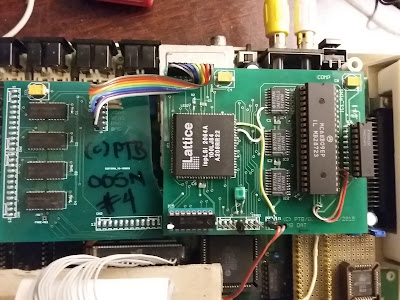

Pictured is a 6809E just for testing.

This is a prototype just to see if the old CPLD code still works (from circa 1998 or so).

Reminiscent of the older "NoCan" series of pcb's.

This should be an exact copy of the NoCan8MB pcb, for software purposes.

Features:

Yellow LED to show 2mhz is on or off.

Yellow LED to show power is on.

Newer pcb will have an LED to show any 8MB activity,

along with a jumper to allow or stop memory above 2MB.

On the left pcb, 4 each 4m x 4 bit drams (8MB total).

With a 8 pin connection to the DAT when desired.

Without the DAT it's just 512K.

On the right pcb is an isolated and buffered CPU

with a 2MB DAT (Lattice CPLD + 74LS189 sram).

The 8 wire cable is for the extra address lines, etc.

The two wire cable going south is for HSYNC and 28MHz from the GIME to keep all in sync.

JTAG connector there too.

The two wires on the right are mistakes and are not needed.

Thanks to http://www.JLCPCB.COM for their great $2 pcb's.

Simulated PCB:

Top Left: ZA9, ZA10 etc. connector.

Bottom Left: 74LS189 sram, JTAG connector, HSYNC and 28MHz connector.

Center Left: Lattice ispLSI-2064A-100LJ94 CPLD.

Stuff on the right is a fully buffered HD63C09EP.

-> The data-buffer shown as a 20-dip is NOT used, but was left in as a prototype test.

Simulated Schematic:

Shows all of the chips as connected.

The 74LS245 is NOT used but left in for testing only.

IdeZilla

aka Paul T Barton

Comments Welcomed

Pictured is a 6809E just for testing.

This is a prototype just to see if the old CPLD code still works (from circa 1998 or so).

Reminiscent of the older "NoCan" series of pcb's.

This should be an exact copy of the NoCan8MB pcb, for software purposes.

Features:

Yellow LED to show 2mhz is on or off.

Yellow LED to show power is on.

Newer pcb will have an LED to show any 8MB activity,

along with a jumper to allow or stop memory above 2MB.

On the left pcb, 4 each 4m x 4 bit drams (8MB total).

With a 8 pin connection to the DAT when desired.

Without the DAT it's just 512K.

On the right pcb is an isolated and buffered CPU

with a 2MB DAT (Lattice CPLD + 74LS189 sram).

The 8 wire cable is for the extra address lines, etc.

The two wire cable going south is for HSYNC and 28MHz from the GIME to keep all in sync.

JTAG connector there too.

The two wires on the right are mistakes and are not needed.

Thanks to http://www.JLCPCB.COM for their great $2 pcb's.

Simulated PCB:

Top Left: ZA9, ZA10 etc. connector.

Bottom Left: 74LS189 sram, JTAG connector, HSYNC and 28MHz connector.

Center Left: Lattice ispLSI-2064A-100LJ94 CPLD.

Stuff on the right is a fully buffered HD63C09EP.

-> The data-buffer shown as a 20-dip is NOT used, but was left in as a prototype test.

Simulated Schematic:

Shows all of the chips as connected.

The 74LS245 is NOT used but left in for testing only.

IdeZilla

aka Paul T Barton

Comments Welcomed

Comments

Post a Comment